飯塚 哲也 教授

本郷キャンパス

大学院工学系研究科・電気系工学専攻

学科電子情報工学科

半導体システム分野

電子デバイス・電子機器

通信・ネットワーク

人工知能

半導体

無線通信(5G/6G)

Internet of Things (IoT)

デザイン・サイエンス 〜回路設計技術を科学し、高性能システムの実現へ〜

アナログ集積回路設計技術(デザイン)に着目し、理論・解析に基づいた(サイエンス)最適設計指針を明らかにすることで、通信・IoT・AI等の応用に向けた高性能集積回路システムの実現を目指しています。

研究分野1

ミリ波集積回路技術

既に実用となっている5G技術そして次世代の6Gと更にその先にある通信・レーダー等の先端応用への適用を目指したミリ波集積回路技術に関する研究を行っています。ミリ波送受信機への応用を目指した発振器、増幅器、変調器と言った要素回路技術を開発し、その設計・試作・評価を通して性能実証を行っています。D-bandと呼ばれる140GHz帯での開発の知見を生かし、300GHz帯など更に高周波を用いた技術開発を推進しています。

研究分野2

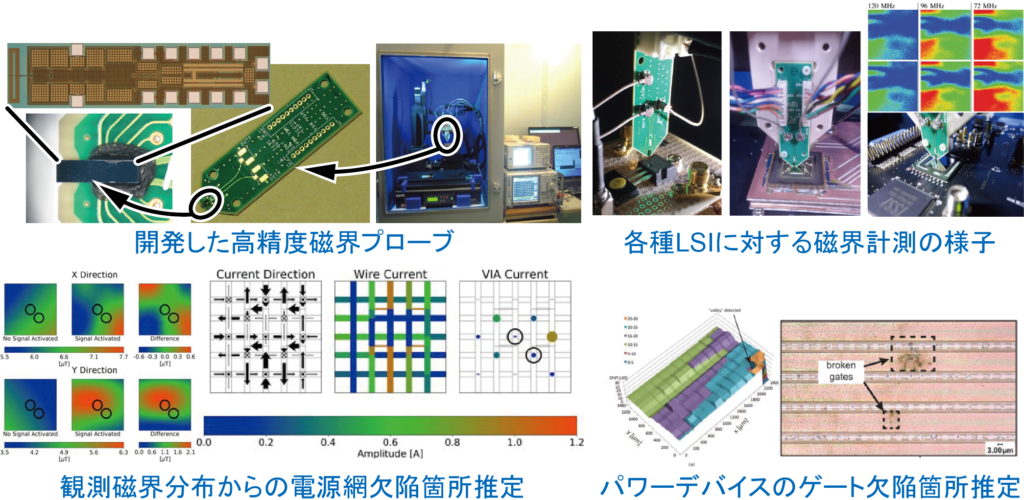

高精度磁界計測・解析技術

集積回路技術が我々にとってより身近なものとなり日常生活にとって必須のものになると同時に、ハードウェアの信頼性やセキュリティ脆弱性が新たな問題として寄り顕在化しています。その反面、先端の極微細集積回路における内部の潜在的な問題を非破壊・非侵襲で発見することは大変困難な課題です。本研究では、集積回路からの放射磁界を高精細かつ高精度に計測し、回路内部状態を正確に推定する手法を開発しました。本研究での知見を生かし、5G通信向けアンテナの性能評価手法などの応用研究なども行っています。

研究分野3

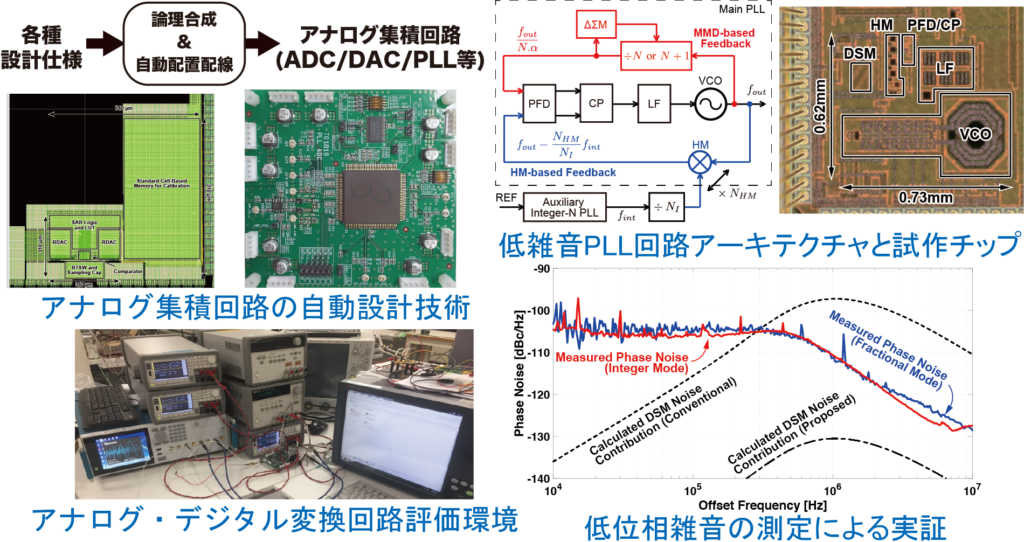

アナログ・デジタル混載回路の高性能化と設計自動化技術

通信・センサ・レーダーなど、広く多くの応用で必須の構成要素であるアナログ-デジタル変換器(ADC)、デジタル-アナログ変換器(DAC)、位相同期回路(PLL)などのアナログ集積システムは、その応用システム全体の性能を律速するため日々性能向上が求められています。次世代アプリケーションへの適用を目指した性能ブレイクスルーを達成するため、集積回路設計技術(デザイン)に対して、理論・解析(サイエンス)に基づいた設計最適化指針を確立し、高性能回路の実現と自動化を通した設計容易化を目指して研究活動を行っています。

研究分野4

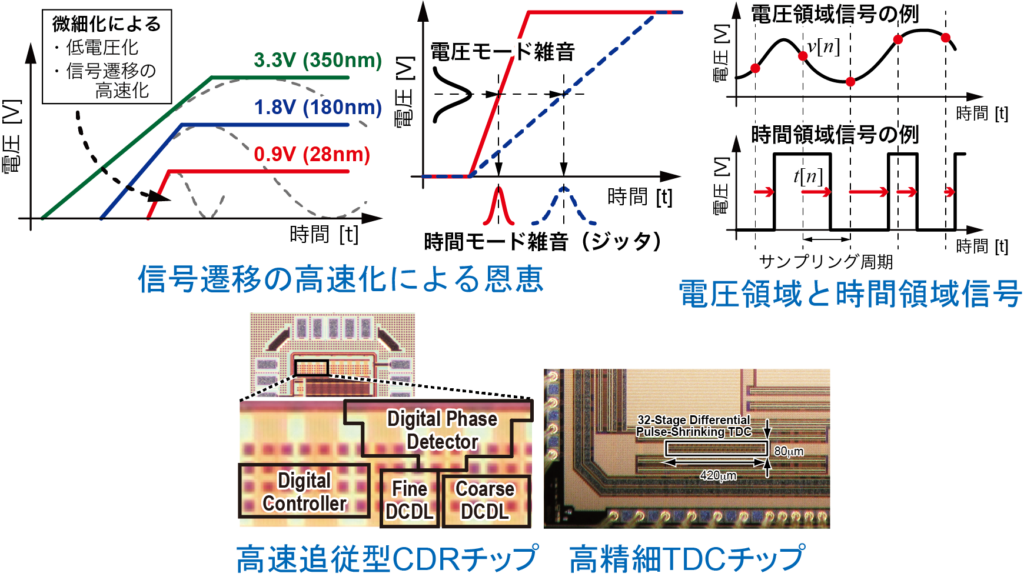

時間領域信号処理技術

集積回路技術の微細化によりトランジスタに代表される集積デバイスの動作速度が高速化するとともに動作電圧が制限されることで、電圧や電流と言った値を情報として用いるよりも、時間方向の値を情報として用いる方が高精度かつ高効率なシステムが実現できると考えられます。時間を情報として取り扱うための基礎となる回路技術である時間-デジタル変換回路や、それを通信に応用したクロック再生技術などを提案し、実証しています。

研究分野5

AI・脳型コンピューティング技術

AI処理の高速化はおもに膨大なエネルギー消費に阻まれて物理的な限界に直面しつつあります。従来のトランジスタに変わる新たなデバイス技術との協奏を通して、次世代性能や計算効率のブレイクスルー達成を目指した研究を複数推進しています。複雑系・バイオエレクトロニクス分野の田畑仁教授グループと共同で、スピン波伝搬・確率共鳴技術を応用した低消費エネルギーかつ高性能なAIデバイスの実現を目指した研究を行っています。また、国立研究開発法人産業技術総合研究所(産総研)や九州大学の研究者とともに、スパイキングニューラルネットワークによるエッジでの高効率コンピューティングの達成に向けた共同研究を行っています。