## 問題A

ここでは組合せ回路のみを考える. チップに対し, できるだけ少ない入力値の集合を与えて出力値を観察することにより, チップで実現している論理関数やチップ内の部分回路で実現している論理関数を同定したい. ここで論理関数の同定とは, 実現している論理関数をユニークに決定することを指す. 以下の間に答えよ. なお論理式内では, 変数は英字1字または英字1字と数字で表す. 否定は~で, 論理和は+で表し, 論理積の演算子は省略する. また, nは自然数とし, AND ゲートと OR ゲートの記号は下記を用いる.

- (1) n入力1出力の論理関数は全部でいくつあるか求め、理由を説明せよ.

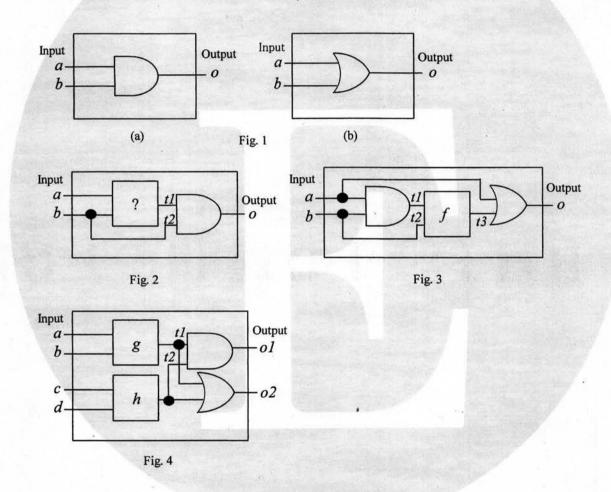

- (2) チップ内部が図1(a)又は(b)のいずれかになっていることが分かっている場合,どのような入力値の集合を与えれば、チップで実現している論理関数を同定できるか、例を1つ示し、それを説明せよ、

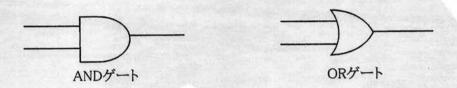

- (3) チップの内部構造に関し、内部構造が不明な部分回路と AND ゲートが図2に示すように接続されていることが分かっている場合、どのような入力値の集合を与えれば、チップで実現している論理関数を同定できるか、例を1つ示し、それを説明せよ.

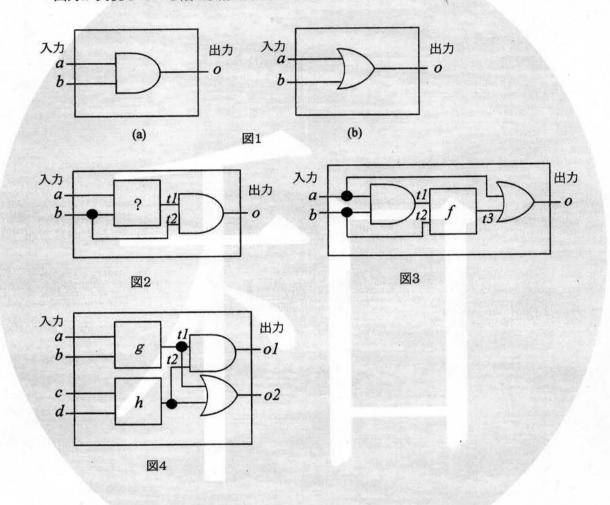

- (4) チップの内部構造に関し、 2 入力の未知の論理関数 f を実現している部分回路と AND ゲート、OR ゲートが図 3 に示すように接続されていることが分かっている場合、以下の間に答えよ、

- (a) t1=1 かつ t2=0 は決して実現できないことを示せ.

- (b) tI = 1 かつ t2 = 1 の場合には、f の出力値はチップの出力値に影響を及ぼさないことを説明せよ.

- (c) チップの出力で、 $a + \sim b$  を実現する全ての論理関数f を真理値表の形で列挙せよ、 実現できない場合は、それを証明せよ、

- (d) 入力  $a \ge b$  の排他的論理和,  $\sim ab + a \sim b$  をチップの出力で実現する全ての論理関数 f を真理値表の形で列挙せよ、実現できない場合は、それを証明せよ、

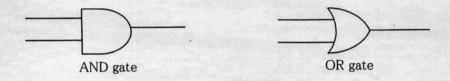

- (5) チップの内部構造に関し、内部構造が不明な2入力の部分回路2つ(それぞれが実現する未知の論理関数をgとhとする)と AND ゲート、OR ゲートが図4に示すように接続されていることが分かっているとする. 以下の問に答えよ.

- (a) 入力値が a=b=c=d=0 の時のチップの出力値が oI=1, o2=1 であった場合,その他にどのような入力値の集合を与えれば,論理関数 g と h を同定できるか,例を1つ示し,それを説明せよ.同定できない場合にはその理由を説明せよ.

- (b) 入力値が a=b=c=d=0 の時のチップの出力値が o1=0, o2=0 であった場合, その他にどのような入力値の集合を与えれば, 論理関数 g と h を同定できるか, 例を 1 つ示し, それを説明せよ. 同定できない場合にはその理由を説明せよ.

- (c) 入力値が a=b=c=d=0 の時のチップの出力値が ol=0, o2=1 であった場合,その他にどのような入力値の集合を与えれば,論理関数 g と h を同定できるか,例を 1 つ示し,それを説明せよ.同定できない場合にはその理由を説明せよ.

- (6) チップは、(n+1)入力1出力とする (n>2). 以下の条件を満たす回路を、n入力1出力の部分回路2つと、3入力1出力の部分回路1つを用いて作成せよ。また条件を満たしている理由も説明せよ。

条件: チップの(n+1)入力のすべての入力値に対する出力値を観察しなければチップの 出力が実現している論理関数を同定できない.

## **Problem A**

Here we consider only combinational circuits. We would like to identify the logic functions realized by the chips or sub-circuits inside the chips by supplying the minimum sets of input patterns to the chips and observing the corresponding output values from the chips. Here, identification of logic functions is to uniquely determine the realized logic function. Answer the following questions. In logic expressions, a variable is represented with an alphabet or an alphabet with a number. Logical negation is represented by " $\sim$ ", logical OR is represented by "+", and logical AND is omitted. Also, n represents a natural number, and the following symbols are used for an AND gate and an OR gate.

- (1) How many possible logic functions are there for n inputs and 1 output? Explain the reason.

- (2) If we know that the internal structure of the chip is either (a) or (b) in Fig. 1, show and explain a set of input patterns which can identify the logic function realized by the chip.

- (3) If we know that the internal structure of the chip is the one shown in Fig. 2, consisting of an unknown sub-circuit and an AND gate, show and explain a set of input patterns which can identify the logic function realized by the chip.

- (4) Assuming that we know that the internal structure of the chip is the one shown in Fig. 3, consisting of an unknown 2-input sub-circuit which realizes the logic function f, an AND gate, and an OR gate, answer the following questions.

- (a) Show that the case where t1 = 1 and t2 = 0 can never be realized.

- (b) Show that the output of f never influences the output of the chip when t1 = 1 and t2 = 1.

- (c) Show all logic functions for f in truth tables which realize  $a + \sim b$  at the output of the chip. If that cannot be realized, show the proof.

- (d) Show all logic functions for f in truth tables which realize exclusive OR of a and b,  $\sim ab + a \sim b$ , at the output of the chip. If that cannot be realized, show the proof.

- (5) Assuming that we know that the internal structure of the chip is the one shown in Fig. 4, consisting of two unknown 2-input sub-circuits which realize the unknown logic functions, g and h, an AND gate, and an OR gate, answer the following questions.

- (a) If the outputs of the chip are o1 = 1, and o2 = 1 when the inputs are a = b = c = d = 0, show an additional set of input patterns which can identify the logic functions realized by g and h, and explain why. If identification is not possible, explain why.

- (b) If the outputs of the chip are o1 = 0, and o2 = 0 when the inputs are a = b = c = d = 0, show an additional set of input patterns which can identify the logic functions realized by g and h, and explain why. If identification is not possible, explain why.

- (c) If the outputs of the chip are o1 = 0, and o2 = 1 when the inputs are a = b = c = d = 0, show an additional set of input patterns which can identify the logic functions realized by g and h, and explain why. If identification is not possible, explain why.

- (6) Consider a chip with (n+1) inputs and 1 output (n > 2). Construct a circuit which satisfies the following condition using two sub-circuits with n inputs and 1 output, and a sub-circuit with 3 inputs and 1 output. Explain why the circuit satisfies the condition.

Condition: the logic function realized by the chip cannot be identified unless all possible values for (n+1) inputs of the chip are supplied.